## 審決

不服 2018-13073

(省略)

請求人 三星ディスプレイ株式會社

(省略)

代理人弁理士 特許業務法人共生国際特許事務所

特願 2017-1414 「表示パネル及びそれを含む表示装置」拒絶査定不服審判事件〔平成 29 年 4 月 13 日出願公開、特開 2017-72858 〕について、次のとおり審決する。

### 結論

本件審判の請求は、成り立たない。

### 理由

#### 第 1 手続の経緯

この審判事件に関する出願（以下、「本願」という。）は、2011年（平成 23 年）2 月 23 日（以下、「優先日」という。）に大韓民国でした特許出願に基づくパリ条約の優先権を主張して平成 24 年 2 月 15 日にした特許出願（特願 2012-30124）の一部を、平成 29 年 1 月 6 日に同優先権の主張を伴う新たな特許出願としたものである。

そして、同年 2 月 2 日に明細書及び特許請求の範囲についての補正がされ、さらに、同年 12 月 29 日に明細書及び特許請求の範囲についての補正（以下、「第 1 次補正」という。）がされるとともに、意見書（以下、「第 1 意見書」という。）が提出され、平成 30 年 5 月 18 日付けで拒絶査定がされ、同 29 日に査定の謄本が送達された。

これに対して、同年 10 月 1 日に拒絶査定不服審判（本件審判）が請求され、同時に明細書及び特許請求の範囲についての補正がされたが、この補正は、令和元年 6 月 20 日付けの決定をもって却下され、同日付けで拒絶の理由（以下、「当審拒絶理由」という。）が通知された。この拒絶理由通知は、特許法第 17 条の 2 第 1 項第 3 号に規定する最後の拒絶理由通知である。

その後、令和元年 9 月 25 日に明細書及び特許請求の範囲についての補正（以下、「本件補正」という。）がされるとともに、意見書（以下、「本件意見書」という。）が提出された。

なお、本件補正前（第 1 次補正後をいう。以下同じ。）の請求項の数は 10 であり、本件補正後の請求項の数は 2 である。

#### 第 2 補正の却下の決定

[補正の却下の決定の結論]

本件補正を却下する。

[補正の却下の決定の理由]

本件補正は、以下に述べるとおり、特許法第17条の2第5項第1号ないし第4号の掲げるいずれの事項を目的とするものでもないから、同法第159条第1項において読み替えて準用する同法第53条第1項の規定により却下するべきものである。

### 1 本件補正の内容

本件補正は、第1の補正事項として、本件補正前の請求項1ないし請求項7及び請求項9を削除するものである。また、第2の補正事項として、本件補正前の請求項8を、その記載の一部を削除し、その記載に本件補正前の請求項3及び請求項9の記載を付加して、本件補正後の請求項1とするものである。さらに、第3の補正事項として、本件補正前の請求項8の記載を引用して記載する本件補正前の請求項10を、本件補正後の請求項1の記載を引用して記載するものに変更して、本件補正後の請求項2とするものである。

したがって、本件補正後の請求項1及び請求項2は、それぞれ本件補正前の請求項8及び請求項10に対応する。

本件補正の第2の補正事項のうち、本件補正前の請求項8の記載の一部の削除及び本件補正前の請求項3の記載の付加は、「第1放電トランジスタ」、「第2放電トランジスタ」、「第i-1ステージ」と「第jステージ」に関する補正事項である。また、本件補正前の請求項9の記載の付加は、「印刷回路基板」に関する補正事項である。

本件補正前の請求項8及び本件補正後の請求項1の記載は、以下のとおりである。参考の便宜を図るため、本件補正前の請求項3及び請求項9の記載も併せて示す。下線は、本件補正の第2の補正事項のうち、「第1放電トランジスタ」と「第2放電トランジスタ」に関する補正事項を示すために、すなわち、本件補正前の請求項8の記載のうち削除されたものと、本件補正前の請求項8の記載に付加された本件補正前の請求項3の記載とを示すために、当合議体が付した。

#### (1) 本件補正前

##### 「【請求項3】

前記第i-1ステージ及び前記第2放電トランジスタは、前記第1画素行の第1及び第2ゲートラインによって定義される前記第1画素行の幅より小さいか又は同じ幅を有するように前記第1周辺領域に形成され、

前記第jステージ及び前記第1放電トランジスタは、前記第2画素行の第1及び第2ゲートラインによって定義される前記第2画素行の幅より小さいか又は同じ幅を有するように前記第2周辺領域内に形成されることを特徴とする請求項1に記載の表示パネル。」

## 「【請求項8】

表示領域に配置され、第1画素行及び第2画素行を含む複数の画素行及び複数の画素列からなる複数の画素と、列方向に伸張され、順次に配列された第 $m - 1$  ( $m$ は自然数) データライン、第 $m$ データライン、第 $m + 1$ データライン、及び第 $m + 2$ データラインを含む複数のデータラインと、行方向に伸長された複数のゲートラインと、前記表示領域の第1周辺領域に形成された第1ゲート駆動回路と、前記第1周辺領域に向き合う前記表示領域の第2周辺領域に形成された第2ゲート駆動回路と、を有する表示パネルと、

前記表示パネルに電気的に接続され、前記第1及び第2ゲート駆動回路に提供する第1クロック信号、第2クロック信号、第3クロック信号、及び第4クロック信号を生成するメイン駆動回路が実装された印刷回路基板と、を備え、

前記第1画素行は、前記第1画素行の第1側部に位置する第1ゲートラインと前記第1画素行の第2側部に位置する第2ゲートラインとの間に配置され、

前記第2画素行は、前記第1画素行に隣接して前記第2画素行の第1側部に位置する第1ゲートラインと前記第2画素行の第2側部に位置する第2ゲートラインとの間に配置され、

前記第1ゲート駆動回路は、前記表示領域の第1周辺領域に形成され、前記第1画素行の第1ゲートラインにゲート信号を提供する第 $i - 1$  ( $i$ は自然数) ステージと、前記第 $i - 1$ ステージに隣接して第2画素行の第1ゲートラインにゲート信号を提供する第 $i$ ステージと、を含み、

前記表示パネルは、前記第 $i - 1$ ステージと前記第 $i$ ステージとの間の前記第1周辺領域に形成され、前記第1画素行の第2ゲートラインに印加されたハイ電圧をロード電圧に放電する第2放電トランジスタを含み、

前記第 $m - 1$ データラインと前記第 $m$ データラインとの間の前記第1画素行の第1画素及び第2画素は、前記第 $m$ データラインに電気的に接続され、

前記第 $m$ データラインと前記第 $m + 1$ データラインとの間の前記第1画素行の第3画素及び第4画素は、前記第 $m + 1$ データラインに電気的に接続され、

前記第 $m + 1$ データラインと前記第 $m + 2$ データラインとの間の前記第1画素行の第5画素及び第6画素は、前記第 $m + 2$ データラインに電気的に接続され、

前記第1画素行の前記第1、第3、及び第6画素は、前記第1画素行の第1側部に位置する前記第1ゲートラインに電気的に接続され、

前記第1画素行の前記第2、第4、及び第5画素は、前記第1画素行の第2側部に位置する前記第2ゲートラインに電気的に接続され、

前記第2ゲート駆動回路は、前記第2周辺領域に形成され、前記第1画素行の第2ゲートラインにゲート信号を提供する第 $j - 1$  ( $j$ は自然数) ステージと、前記第 $j - 1$ ステージに隣接する前記第2周辺領域に形成され、前記第2画素行の第2ゲートラインにゲート信号を提供する第 $j$ ステージと、を含み、

前記表示パネルは、前記第 $j - 1$ ステージと前記第 $j$ ステージとの間の前記第2周辺領域に形成され、前記第2画素行の第1ゲートラインに印加されたハイ電圧をロード電圧に放電する第1放電トランジスタを更に含み、

前記第1放電トランジスタは、行方向で第2放電トランジスタに重ならない

ことを特徴とする表示装置。

【請求項9】

前記印刷回路基板は、

前記第1及び第2クロック信号を前記第1ゲート駆動回路に伝達するための第1信号配線と、

前記第3及び第4クロック信号を前記第2ゲート駆動回路に伝達するための第2信号配線と、

前記第1及び第2信号配線の時定数値を制御するRC制御部と、を含むことを特徴とする請求項8に記載の表示装置。」

(2) 本件補正後

「【請求項1】

表示領域に配置され、第1画素行及び第2画素行を含む複数の画素行及び複数の画素列からなる複数の画素と、列方向に伸張され、順次に配列された第 $m - 1$  ( $m$ は自然数) データライン、第 $m$ データライン、第 $m + 1$ データライン、及び第 $m + 2$ データラインを含む複数のデータラインと、行方向に伸長された複数のゲートラインと、前記表示領域の第1周辺領域に形成された第1ゲート駆動回路と、前記第1周辺領域に向き合う前記表示領域の第2周辺領域に形成された第2ゲート駆動回路と、を有する表示パネルと、

前記表示パネルに電気的に接続され、前記第1及び第2ゲート駆動回路に提供する第1クロック信号、第2クロック信号、第3クロック信号、及び第4クロック信号を生成するメイン駆動回路が実装された印刷回路基板と、を備え、

前記第1画素行は、前記第1画素行の第1側部に位置する第1ゲートラインと前記第1画素行の第2側部に位置する第2ゲートラインとの間に配置され、

前記第2画素行は、前記第1画素行に隣接して前記第2画素行の第1側部に位置する第1ゲートラインと前記第2画素行の第2側部に位置する第2ゲートラインとの間に配置され、

前記第1ゲート駆動回路は、前記表示領域の第1周辺領域に形成され、前記第1画素行の第1ゲートラインにゲート信号を提供する第 $i - 1$  ( $i$ は自然数) ステージと、前記第 $i - 1$ ステージに隣接して第2画素行の第1ゲートラインにゲート信号を提供する第 $i$ ステージと、を含み、

前記表示パネルは、前記第 $i - 1$ ステージと前記第 $i$ ステージとの間の前記第1周辺領域に形成され、前記第1画素行の第2ゲートラインに印加されたハイ電圧をロー電圧に放電する第2放電トランジスタを含み、

前記第 $m - 1$ データラインと前記第 $m$ データラインとの間の前記第1画素行の第1画素及び第2画素は、前記第 $m$ データラインに電気的に接続され、

前記第 $m$ データラインと前記第 $m + 1$ データラインとの間の前記第1画素行の第3画素及び第4画素は、前記第 $m + 1$ データラインに電気的に接続され、

前記第 $m + 1$ データラインと前記第 $m + 2$ データラインとの間の前記第1画素行の第5画素及び第6画素は、前記第 $m + 2$ データラインに電気的に接続され、

前記第1画素行の前記第1、第3、及び第6画素は、前記第1画素行の第1

側部に位置する前記第1ゲートラインに電気的に接続され、

前記第1画素行の前記第2、第4、及び第5画素は、前記第1画素行の第2側部に位置する前記第2ゲートラインに電気的に接続され、

前記第2ゲート駆動回路は、前記第2周辺領域に形成され、前記第1画素行の第2ゲートラインにゲート信号を提供する第 $j - 1$ （ $j$ は自然数）ステージと、前記第 $j - 1$ ステージに隣接する前記第2周辺領域に形成され、前記第2画素行の第2ゲートラインにゲート信号を提供する第 $j$ ステージと、を含み、

前記表示パネルは、前記第 $j - 1$ ステージと前記第 $j$ ステージとの間の前記第2周辺領域に形成され、前記第2画素行の第1ゲートラインに印加されたハイ電圧をロー電圧に放電する第1放電トランジスタを更に含み、

前記第 $i - 1$ ステージ及び前記第2放電トランジスタは、前記第1画素行の第1及び第2ゲートラインによって定義される前記第1画素行の幅より小さいか又は同じ幅を有するように前記第1周辺領域に形成され、

前記第 $j$ ステージ及び前記第1放電トランジスタは、前記第2画素行の第1及び第2ゲートラインによって定義される前記第2画素行の幅より小さいか又は同じ幅を有するように前記第2周辺領域内に形成され、

前記印刷回路基板は、

前記第1及び第2クロック信号を前記第1ゲート駆動回路に伝達するための第1信号配線と、

前記第3及び第4クロック信号を前記第2ゲート駆動回路に伝達するための第2信号配線と、

前記第1及び第2信号配線の時定数値を制御するRC制御部と、を含むことを特徴とする表示装置。」

## 2 本件補正の目的

### (1) 判断

ア 本件補正の第2の補正事項のうち、「第1放電トランジスタ」、「第2放電トランジスタ」、「第 $i - 1$ ステージ」と「第 $j$ ステージ」に関する補正事項は、具体的には、「前記第1放電トランジスタは、行方向で第2放電トランジスタに重ならない」という記載（以下、「補正前記載」という。）を削除し、「前記第 $i - 1$ ステージ及び前記第2放電トランジスタは、前記第1画素行の第1及び第2ゲートラインによって定義される前記第1画素行の幅より小さいか又は同じ幅を有するように前記第1周辺領域に形成され、」という記載（以下、「補正後記載1」という。）及び「前記第 $j$ ステージ及び前記第1放電トランジスタは、前記第2画素行の第1及び第2ゲートラインによって定義される前記第2画素行の幅より小さいか又は同じ幅を有するように前記第2周辺領域内に形成され、」という記載（以下、「補正後記載2」という。）を付加するものである。

イ 補正前記載では、行方向における「第1放電トランジスタ」と「第2放電トランジスタ」との位置関係が特定されている。

一方、補正後記載1では、「第 $i - 1$ ステージ」と「第2放電トランジス

タ」の幅と「第1画素行の第1及び第2ゲートラインによって定義される」「第1画素行の幅」との大小関係が特定されている。同様に、補正後記載2では、「第jステージ」と「第1放電トランジスタ」の幅と「第2画素行の第1及び第2ゲートラインによって定義される」「第2画素行の幅」との大小関係が特定されている。

すなわち、「第1放電トランジスタ」、「第2放電トランジスタ」、「第i-1ステージ」と「第jステージ」に関する補正事項は、行方向における「第1放電トランジスタ」と「第2放電トランジスタ」との位置関係の特定を削除し、「第i-1ステージ」と「第2放電トランジスタ」の幅と「第1画素行の第1及び第2ゲートラインによって定義される」「第1画素行の幅」との大小関係並びに「第jステージ」と「第1放電トランジスタ」の幅と「第2画素行の第1及び第2ゲートラインによって定義される」「第2画素行の幅」との大小関係の特定を付加するものである。

しかし、位置関係の特定と大小関係の特定とでは、特定の観点が全く異なるし、補正後記載1及び補正後記載2の大小関係の特定により、補正前記載の位置関係の特定が、本件補正後も実質的に維持されているとは認められない。したがって、行方向における「第1放電トランジスタ」と「第2放電トランジスタ」との位置関係に代えて、「第i-1ステージ」と「第2放電トランジスタ」の幅と「第1画素行の第1及び第2ゲートラインによって定義される」「第1画素行の幅」との大小関係並びに「第jステージ」と「第1放電トランジスタ」の幅と「第2画素行の第1及び第2ゲートラインによって定義される」「第2画素行の幅」との大小関係を特定しても、行方向における「第1放電トランジスタ」と「第2放電トランジスタ」との位置関係が、本件補正前に比べて限定されることにはならない。また、行方向における「第1放電トランジスタ」と「第2放電トランジスタ」との位置関係の不明瞭さが正されることにもならない。

ウ そうすると、本件補正の第2の補正事項のうち、「第1放電トランジスタ」、「第2放電トランジスタ」、「第i-1ステージ」と「第jステージ」に関する補正事項は、特許請求の範囲の減縮を目的とするものには該当しないし、明瞭でない記載の釈明を目的とするものにも該当しない。請求項の削除を目的とするものにも、誤記の訂正を目的とするものにも該当しないことは、明らかである。

## (2) 請求人の主張について

請求人は、本件意見書で、本件補正是請求項の統合による構成要素の限定的減縮及び明瞭でない記載の釈明を目的として請求項を明細書の記載に合わせるものであると主張する。

しかし、本件補正是、本件補正前の請求項8の記載に本件補正前の請求項3の記載（補正後記載1及び補正後記載2）並びに本件補正前の請求項9の記載を付加するだけでなく、本件補正前の請求項8の記載の一部（補正前記載）を削除するものであるから、請求項の統合であると直ちにいうことはできない。

そして、補正前記載を削除して補正後記載1及び補正後記載2を付加する補正が、特許請求の範囲の減縮を目的とするものにも、明瞭でない記載の釈明を目的とするものにも該当しないことは、前記(1)のとおりである。

したがって、請求人の主張は、採用することができない。

### 3 補正の却下の決定のむすび

以上のとおりであるから、本件補正是、特許法第17条の2第5項第1号ないし第4号の掲げるいずれの事項を目的とするものでもない。

したがって、本件補正是、同法第159条第1項において読み替えて準用する同法第53条第1項の規定により却下するべきものである。

よって、補正の却下の決定の結論のとおり決定する。

## 第3 本願についての判断

### 1 特許請求の範囲の記載

前記第2のとおり、本件補正是却下されたので、本願の特許請求の範囲の記載は、第1次補正後の特許請求の範囲の記載のとおりであり、特に第1次補正後の請求項1の記載は、以下のとおりである。

なお、以下では、第1次補正後の請求項1に記載された事項により特定される発明を「本願発明」という。

#### 「【請求項1】

表示領域に配置され、第1画素行及び第2画素行を含む複数の画素と、

列方向に伸長され、順次に配列された第m-1(mは自然数)データライン、第mデータライン、第m+1データライン、及び第m+2データラインを含む複数のデータラインと、

行方向に伸長された複数のゲートラインと、を有し、

前記第1画素行は、前記第1画素行の第1側部に位置する第1ゲートラインと前記第1画素行の第2側部に位置する第2ゲートラインとの間に配置され、

前記第2画素行は、前記第2画素行の第1側部に位置する第1ゲートラインと前記第2画素行の第2側部に位置する第2ゲートラインとの間に配置され、

前記表示領域の第1周辺領域に形成され、第1画素行の第1ゲートラインにゲート信号を提供する第i-1(iは自然数)ステージと、

前記第i-1ステージに隣接する前記第1周辺領域に形成され、前記第2画素行の第1ゲートラインにゲート信号を提供する第iステージと、

前記第i-1ステージと前記第iステージとの間の前記第1周辺領域に形成され、前記第1画素行の第2ゲートラインに印加されたハイ電圧をロー電圧に放電する第2放電トランジスタと、を含み、

前記第m-1データラインと前記第mデータラインとの間の前記第1画素行の第1画素及び第2画素は、前記第mデータラインに電気的に接続され、

前記第mデータラインと前記第m+1データラインとの間の前記第1画素行の第3画素及び第4画素は、前記第m+1データラインに電気的に接続され、

前記第m+1データラインと前記第m+2データラインとの間の前記第1画

素行の第5画素及び第6画素は、前記第m+2データラインに電気的に接続され、

前記第1画素行の前記第1、第3、及び第6画素は、前記第1画素行の第1側部に位置する第1ゲートラインに電気的に接続され、

前記第1画素行の前記第2、第4、及び第5画素は、前記第1画素行の第2側部に位置する第2ゲートラインに電気的に接続され、

前記第1周辺領域に向き合う前記表示領域の第2周辺領域に形成され、前記第1画素行の第2ゲートラインにゲート信号を提供する第j-1(jは自然数)ステージと、

前記第j-1ステージに隣接する前記第2周辺領域に形成され、前記第2画素行の第2ゲートラインにゲート信号を提供する第jステージと、

前記第j-1ステージと前記第jステージとの間の前記第2周辺領域に形成され、前記第2画素行の第1ゲートラインに印加されたハイ電圧をロー電圧に放電する第1放電トランジスタと、を更に含み、

前記第1放電トランジスタは、行方向で第2放電トランジスタに重ならないことを特徴とする表示パネル。」

## 2 当審拒絶理由の概要

### (1) 理由1(新規事項)

第1次補正後の請求項1に記載された「第1放電トランジスタは、行方向で第2放電トランジスタに重ならない」という事項は、本願の願書に最初に添付した明細書、特許請求の範囲又は図面に記載した事項であるということができない。

すなわち、第1次補正は、本願の願書に最初に添付した明細書、特許請求の範囲又は図面に記載した事項の範囲内においてしたものでないから、特許法第17条の2第3項に規定する要件を満たしていない。

### (2) 理由2(進歩性)

本願発明は、引用文献1ないし引用文献4、引用文献6及び引用文献7に記載された発明に基づいて、当業者が容易に発明をすることができたものであるから、特許法第29条第2項の規定により特許を受けることができない。

引用文献1：特開2009-151258号公報

引用文献2：米国特許出願公開第2010/0156954号明細書

引用文献3：特開2010-20279号公報

引用文献4：特開2007-72463号公報

引用文献6：特開2006-337710号公報

引用文献7：特開2005-122183号公報

## 3 理由1(新規事項)について

第1次補正後の請求項1には、「第1放電トランジスタは、行方向で第2放電トランジスタに重ならない」という事項が記載されている。

しかし、本願の願書に最初に添付した明細書、特許請求の範囲及び図面（以下、「当初明細書等」という。）には、この事項に相当する記載は見当たらぬ。

請求人は、第1意見書で、この事項の根拠は当初明細書等の【0073】ないし【0079】及び図12の記載であると主張するので、検討する。

#### （1）当初明細書等の記載

当初明細書等の【0073】ないし【0079】及び図12の記載は、以下のとおりである。下線は、当合議体が付した。

#### 「【0073】

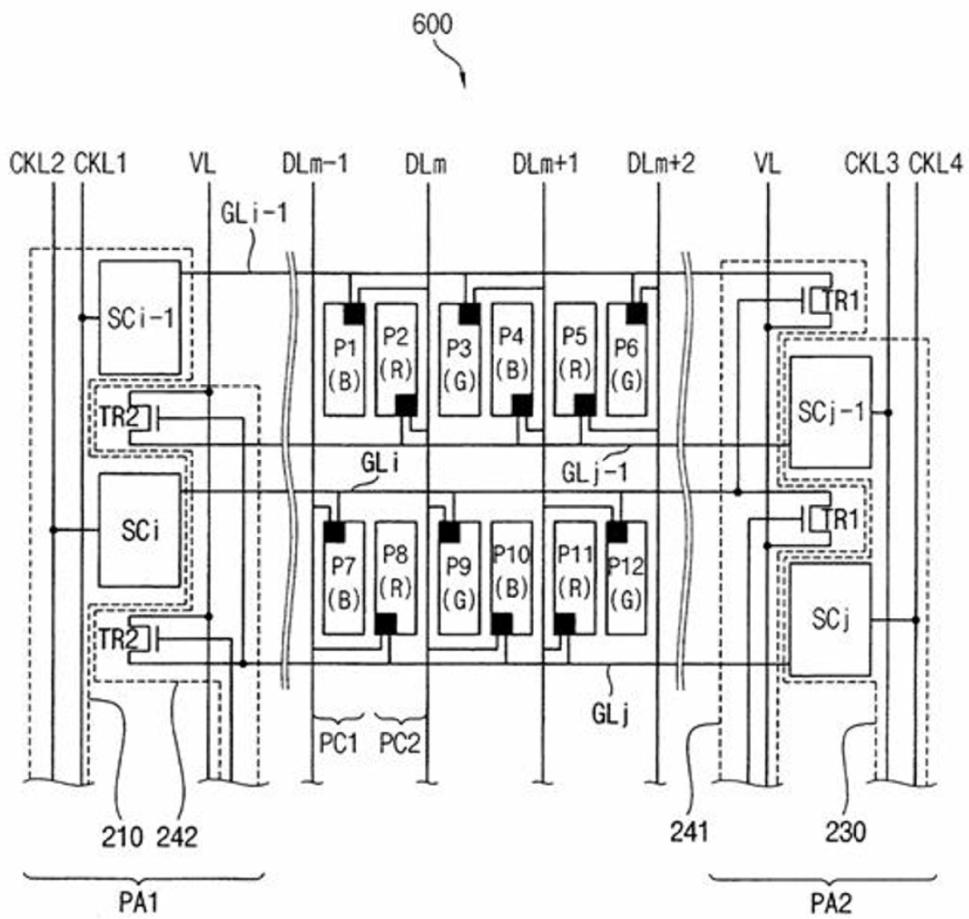

図12は、本発明の他の実施形態による表示パネルを説明するための概念図である。

図1、図4及び図12を参考すれば、本実施形態による表示パネル600は第1及び第2周辺領域PA1、PA2に各々、第1及び第2ゲート駆動回路210、230に加えて、第2及び第1放電回路242、241を含む。

#### 【0074】

第1ゲート駆動回路210は第1周辺領域PA1に形成された複数のステージ(SCi-1, SCi)を含み、各ステージはある画素行の第1側部に配置されたゲートライン(GLi-1, GLi)にゲート信号を提供する。第1ゲート駆動回路210はゲートライン(GLi-1, GLi)の第1周辺領域PA1側の一端と電気的に接続される。

#### 【0075】

第1放電回路241は第2周辺領域PA2に形成される。第1放電回路241は各画素行の第1側部のゲートラインに電気的に接続され、ゲートラインに印加されたゲート信号のハイ電圧VONをロー電圧VOFFで放電させる。第1放電回路241は第1放電トランジスタTR1及びロー電圧VOFFが印加された電圧配線VLを含む。第1放電トランジスタTR1は図示したように、ステージ(SCj-1, SCj)間の第2周辺領域PA2に形成され、第(i-1)及び第(j-1)ゲートラインGLi-1, GLj-1が定義する画素行の幅に対応する第2周辺領域PA2内に形成される。

#### 【0076】

第1放電トランジスタTR1は第1制御電極、第1入力電極、及び第1出力電極を含む。第1制御電極は、第iステージSCiと接続された第iゲートラインGLiと接続し、第1入力電極は第(i-1)ゲートラインGLi-1と接続し、第1出力電極は電圧配線VLと接続する。第1放電トランジスタTR1は第iゲートラインGLiにハイ電圧VONが印加されればターンオンされて第(i-1)ゲートラインGLi-1に印加されたし電圧VONをロー電圧VOFFで放電する。

#### 【0077】

第2ゲート駆動回路230は第1周辺領域PA1に形成された複数のステージ(SCj-1, SCj)を含み、各ステージはある画素行の第2側部に配置

されたゲートライン ( $GL_j - 1, GL_j$ ) にゲート信号を提供する。第2ゲート駆動回路 230 はゲートライン ( $GL_j - 1, GL_j$ ) の第2周辺領域 PA2 側の一端と電気的に接続される。

#### 【0078】

第2放電回路 242 は第1周辺領域 PA1 に形成される。第2放電回路 242 は各画素行の第2側部のゲートラインに電気的に接続され、ゲートラインに印加されたゲート信号のハイ電圧 VON をロー電圧 VOFF で放電させる。第2放電回路 242 は第2放電トランジスタ TR2 及びロー電圧 VOFF が印加された電圧配線 VL を含む。第2放電トランジスタ TR2 は図示したように、ステージ ( $SC_i - 1, SC_i$ ) 間の第1周辺領域 PA1 に形成され、第 ( $i - 1$ ) 及び第 ( $j - 1$ ) ゲートライン  $GL_{i-1}, GL_{j-1}$  が定義する画素行の幅に対応する第1周辺領域 PA1 内に形成される。

#### 【0079】

第2放電トランジスタ TR2 は第2制御電極、第2入力電極、及び第2出力電極を含む。例えば、第2制御電極は第  $j$  ステージ  $SC_j$  と接続された第  $j$  ゲートライン  $GL_j$  と接続し、第2入力電極は第 ( $j - 1$ ) ゲートライン  $GL_{j-1}$  と接続し、第2出力電極は電圧配線 VL と接続する。第2放電トランジスタ TR2 は第  $j$  ゲートライン  $GL_j$  にハイ電圧 VON が印加されればターンオンされて第 ( $j - 1$ ) ゲートライン  $GL_{j-1}$  に印加されたハイ電圧 VON をロー電圧 VOFF で放電する。」

「【図12】

」

## (2) 判断

ア 当初明細書等の前記(1)の記載(特に下線を付した部分)によれば、第1放電トランジスタTR1及び第2放電トランジスタTR2の形成について、以下のことが認められる。

(ア) 第1周辺領域PA1にはステージSCi-1及びステージSCiが形成され(【0074】)、ステージSCi-1とステージSCiとの間に第2放電トランジスタTR2が形成される(【0078】)。

同様に、第2周辺領域PA2にはステージSCj-1及びステージSCjが形成され(【0077】)、ステージSCj-1とステージSCjとの間に第1放電トランジスタTR1が形成される(【0075】)。

なお、「第1周辺領域PA1に形成された複数のステージ(SCj-1, SCj)」という記載(【0077】)は、「第1周辺領域PA1に形成された複数のステージ(SCi-1, SCi)」という記載(【0074】)との対比により、また、図12に示された符号「SCj-1」、「SCj」及び「PA2」の位置関係に照らして、「第2周辺領域PA2に形成された複数のステージ(SCj-1, SCj)」の誤記であることが明らかである。

(イ) 第1放電トランジスタTR1は、第(i-1)及び第(j-1)ゲートラインGLi-1、GLj-1が定義する画素行の幅に対応する第2周辺領域PA2内に形成される(【0075】)。

同様に、第2放電トランジスタTR2は、第(i-1)及び第(j-1)ゲートラインGLi-1、GLj-1が定義する画素行の幅に対応する第1周辺領域PA1内に形成される(【0078】)。

イ まず、前記ア(ア)によれば、第2放電トランジスタTR2が形成される位置は、第1周辺領域PA1に形成されたステージSCi-1及びステージSCiとの関係で特定されており、同様に、第1放電トランジスタTR1が形成される位置は、第2周辺領域PA2に形成されたステージSCj-1及びステージSCjとの関係で特定されている。

しかし、第1周辺領域PA1に形成されたステージSCi-1及びステージSCiと、第2周辺領域PA2に形成されたステージSCj-1及びステージSCjとが、どのような位置関係にあるかについては、当初明細書等に記載されていない。

したがって、第2放電トランジスタTR2の位置がステージSCi-1及びステージSCiとの関係で、第1放電トランジスタTR1の位置がステージSCj-1及びステージSCjとの関係で、それぞれ特定されているとしても、第2放電トランジスタTR2と第1放電トランジスタTR1との位置関係は、何ら特定されない。

そうすると、前記ア(ア)に基づいて、第1放電トランジスタTR1と第2放電トランジスタTR2とが行方向で重ならないということはできない。

ウ 次に、前記ア(イ)によれば、第1放電トランジスタTR1及び第2放電トランジスタTR2は、それぞれ第2周辺領域PA2及び第1周辺領域PA1に形成されるという違いはあるものの、いずれも第(i-1)及び第(j-1)ゲートラインGLi-1、GLj-1が定義する画素行の幅に対応する周辺領域内に形成される。

ここで、「第(i-1)及び第(j-1)ゲートラインGLi-1、GLj-1が定義する画素行の幅に対応する周辺領域内に形成される」とは、当初明細書等の記載に基づいて検討すると、以下に述べるとおり、「前記第1ステージ及び前記第2放電トランジスタは、前記第1及び第2ゲートラインによって定義される画素行の幅より小さいか又は同じ幅を有するように前記第1周辺領域に形成され、前記第2ステージ及び前記第1放電トランジスタは、前記画素行の幅より小さいか又は同じ幅を有するように前記第2周辺領域内に形成される」(【0008】)という趣旨である。

(ア) 本願に係る発明の目的は、隣接した二つの画素が一つのデータラインを共有する構造を採用すると、データ駆動回路の個数を減らすことができる反面、一つの画素行の駆動に必要な二つのゲート信号を生成するために二つの回路ステージが必要となるので、回路ステージを形成する周辺領域の面積が増加し、

表示装置のベーゼル幅が増加するという課題を解決することである（【0003】、【0004】、【0006】）。

（イ）本願に係る発明は、一つの画素行の第1側部に第1ゲートラインを、第2側部に第2ゲートラインを、それぞれ設け、第1ゲートラインにゲート信号を提供する第1ステージを含む第1ゲート駆動回路を第1周辺領域に、第2ゲートラインにゲート信号を提供する第2ステージを含む第2駆動回路を第2周辺領域に、それぞれ設けることにより、前記（ア）の課題を解決するものである（【0008】、【0011】）。

（ウ）第1ステージ及び第2ステージは、いずれも第1ゲートライン及び第2ゲートラインによって定義される画素行の幅より小さいかそれと同じ幅を有するように、それぞれ第1周辺領域及び第2周辺領域に形成される（【0008】）。

第1ステージの幅及び第2ステージの幅にこのような条件を課す理由は、当初明細書等に記載されていない。

しかし、第1ゲート駆動回路も第2ゲート駆動回路も、互いに縦続接続された複数のステージを含むことに鑑みると（【0020】、【0022】）、第1ステージの幅及び第2ステージの幅に前記の条件を課す理由は、複数の第1ステージ及び複数の第2ステージが、それぞれ第1周辺領域及び第2周辺領域内で1列に並ぶようになるためであることが理解される。仮に第1ステージの幅及び第2ステージの幅が画素行の幅より大きいとすれば、複数の第1ステージ及び複数の第2ステージをそれぞれ第1周辺領域及び第2周辺領域内で1列に並べることは不可能であり、表示装置のベーゼル幅が増加するという課題を解決するという本願に係る発明の目的（前記（ア））に反することになるからである。

そして、これに対応する具体的な構成として、当初明細書等の【0014】ないし【0042】及び図1ないし図4に記載された実施形態では、第1ゲート駆動回路210の第(i-1)ステージSC<sub>i-1</sub>及び第iステージSC<sub>i</sub>の幅W<sub>1</sub>も、第2ゲート駆動回路230の第(j-1)ステージSC<sub>j-1</sub>及び第jステージSC<sub>j</sub>の幅W<sub>1</sub>も、2本のゲートラインにより定義される画素行（第1画素行PL<sub>1</sub>、第2画素行PL<sub>2</sub>）の幅W<sub>2</sub>より大きくないとされている（【0020】ないし【0023】）。

（エ）ところで、第1ゲート駆動回路及び第2ゲート駆動回路に加えて、第1放電トランジスタを含む第1放電回路及び第2放電トランジスタを含む第2放電回路をさらに含む場合、「前記第1ステージ及び前記第2放電トランジスタは、前記第1及び第2ゲートラインによって定義される画素行の幅より小さいか又は同じ幅を有するように前記第1周辺領域に形成され、前記第2ステージ及び前記第1放電トランジスタは、前記画素行の幅より小さいか又は同じ幅を有するように前記第2周辺領域内に形成される」（【0008】）。

第1ステージ及び第2放電トランジスタの幅や、第2ステージ及び第1放電

トランジスタの幅にこのような条件を課す理由は、当初明細書等に記載されていない。

しかし、第1ゲート駆動回路も第2ゲート駆動回路も、互いに継続接続された複数のステージを含み、放電トランジスタが2つのステージの間に形成されることに鑑みると（【0074】、【0075】、【0077】、【0078】）、第1ステージ及び第2放電トランジスタの幅や、第2ステージ及び第1放電トランジスタの幅に前記の条件を課す理由は、前記（ウ）で述べたものと同様であると理解される。すなわち、複数の第1ステージとそれらの間に形成される第2放電トランジスタとが第1周辺領域内で1列に並び、複数の第2ステージとそれらの間に形成される第1放電トランジスタとが第2周辺領域内で1列に並ぶようになるためである。

そして、これに対応する具体的な構成として、当初明細書等の【0073】ないし【0079】及び図12に記載された実施形態では、前記ア（イ）のとおり、第1放電トランジスタTR1及び第2放電トランジスタTR2が、いずれも第(i-1)及び第(j-1)ゲートラインGLi-1、GLj-1が定義する画素行の幅に対応する周辺領域内に形成されているものと解される（【0075】、【0078】）。

そうすると、「第(i-1)及び第(j-1)ゲートラインGLi-1、GLj-1が定義する画素行の幅に対応する周辺領域内に形成される」とは、「前記第1ステージ及び前記第2放電トランジスタは、前記第1及び第2ゲートラインによって定義される画素行の幅より小さいか又は同じ幅を有するように前記第1周辺領域に形成され、前記第2ステージ及び前記第1放電トランジスタは、前記画素行の幅より小さいか又は同じ幅を有するように前記第2周辺領域内に形成される」（【0008】）という趣旨であると解するのが相当である。

エ そうすると、前記ア（イ）によれば、第1放電トランジスタTR1及び第2放電トランジスタTR2の幅が、第(i-1)及び第(j-1)ゲートラインGLi-1、GLj-1が定義する画素行の幅との関係で特定されるだけで、第1放電トランジスタTR1と第2放電トランジスタTR2との位置関係は、何ら特定されない。

したがって、前記ア（イ）に基づいて、第1放電トランジスタTR1と第2放電トランジスタTR2とが行方向で重ならないということはできない。

オ 仮に、当初明細書等の記載を離れて、前記ア（イ）によって、第1放電トランジスタTR1及び第2放電トランジスタTR2が、いずれも、第(i-1)及び第(j-1)ゲートラインGLi-1、GLj-1が定義する画素行の内側にあることが特定されていると解したとしても、第1放電トランジスタTR1及び第2放電トランジスタTR2の画素行の幅方向の位置は何ら特定されないから、両者が行方向で重ならないということはできないことに変わりはない。

カ さらに、当初明細書等の図12を参照すると、「第1放電トランジスタT

「R 1」と「第2放電トランジスタTR 2」とは、一見すると、行方向（図12の左右方向）で重なっていない。

しかし、一般に、特許出願の願書に添付される図面は、明細書の記載内容を補完し、特許を受けようとする発明に係る技術内容を当業者に理解させるための説明図であるから、当該発明の技術内容を理解するために必要な程度の正確さを備えていれば足り、部材の大きさや配置に関し、設計図面に要求されるような正確性をもって描かれているとは限らない。

そして、本願に係る発明は、隣接した二つの画素が一つのデータラインを共有する構造を採用すると、表示装置のベゼル幅が増加するという課題を、第1ゲートラインにゲート信号を提供する第1ステージを含む第1ゲート駆動回路を第1周辺領域に、第2ゲートラインにゲート信号を提供する第2ステージを含む第2駆動回路を第2周辺領域に、それぞれ設けることにより解決するものである（前記ウ（ア）及び（イ））。

そうすると、「本発明の他の実施形態による表示パネルを説明するための概念図」（【0073】）である図12によって、第1ゲート駆動回路210が第1周辺領域PA1に、第2駆動回路230が第2周辺領域PA2に、それぞれ設けられていることは理解できるとしても、第1放電トランジスタTR1と第2放電トランジスタTR2とが行方向で重なっているか否かといった、本願に係る発明の課題及び解決手段に直接関係のない技術事項まで認識するべきものではない。

したがって、図12の記載に基づいて、第1放電トランジスタTR1と第2放電トランジスタTR2とが行方向で重ならないということはできない。

キ 以上のとおりであるから、当初明細書等の【0073】ないし【0079】及び図12の記載から、第1放電トランジスタTR1と第2放電トランジスタTR2とが行方向で重ならないということはできない。

### （3）理由1についてのまとめ

以上に述べたとおり、当初明細書等の【0073】ないし【0079】及び図12の記載からは、第1放電トランジスタTR1と第2放電トランジスタTR2とが行方向で重ならないということはできない。また、当初明細書等のその他の箇所にも、第1放電トランジスタTR1と第2放電トランジスタTR2とが行方向で重ならない旨の記載は見当たらない。

そうすると、第1次補正後の請求項1に記載された「第1放電トランジスタは、行方向で第2放電トランジスタに重ならない」という事項は、当初明細書等の全ての記載を総合することにより導かれる技術的事項との関係において、新たな技術的事項を導入しないものということはできない。

したがって、第1次補正是、当初明細書等に記載した事項の範囲内においてしたものではないから、特許法第17条の2第3項に規定する要件を満たしていない。

## 4 理由2（進歩性）について

(1) 引用文献1に記載された発明

ア 引用文献1には、以下の記載がある。下線は、当合議体が付した。

(ア) 実施の形態1

【0014】

(実施の形態1)

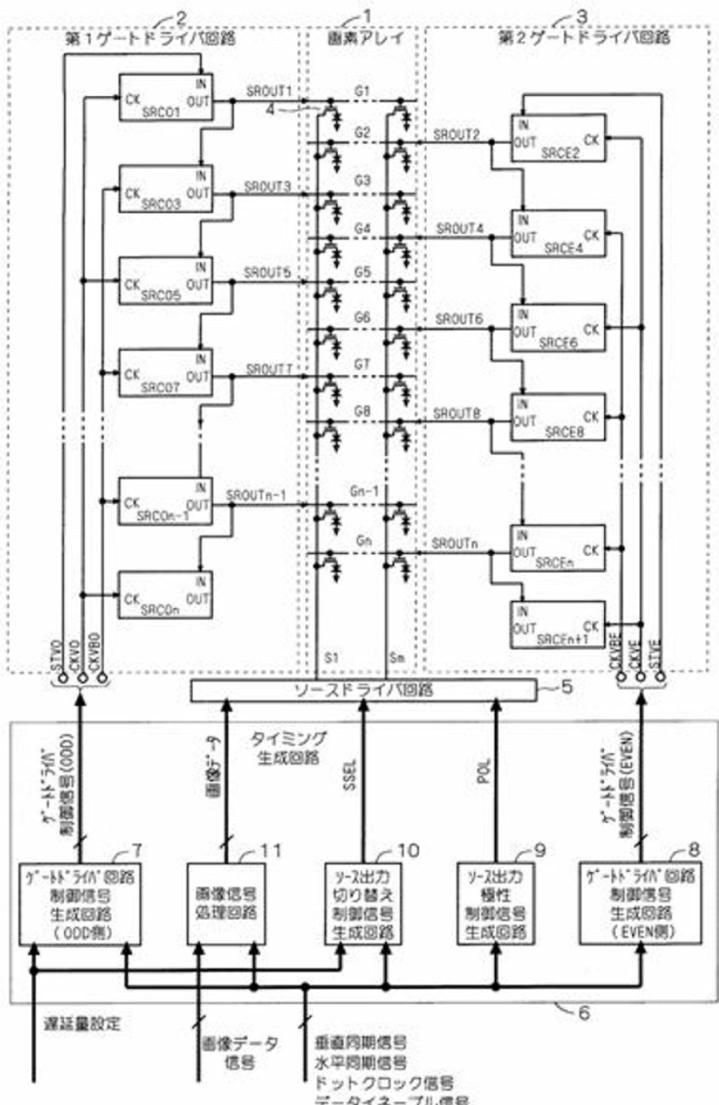

図2に、本実施の形態に係る画像表示装置のブロック図を示す。図2に示す画像表示装置は、TFTにより画素を駆動する液晶表示装置であるとして説明するが、本発明に係る画像表示装置は、液晶表示装置に限られず、同様の構成を有する有機EL表示装置等にも適用することができる。

【0015】

まず、図2に示す画素アレイ1には、m列×n行の画素4が設けられ、それぞれの画素はTFTにより駆動される。なお、画素アレイ1の先頭のゲート線(図中の最上行)をG1、最終のゲート線(図中の最下行)をGn、最左のソース線をS1、最右のソース線をSmとする。

【0016】

図2に示す第1ゲートドライバ回路2は、ゲート線G1を開始行、ゲート線Gn-1を終了行とし、開始行から終了行の方向に奇数行のゲート線をスキャンするシフトレジスタ回路SRCO1～SRCOnを備えている。この第1ゲートドライバ回路2は、アモルファスシリコンTFTで構成されている。

…（中略）…

【0018】

図2に示す第2ゲートドライバ回路3は、ゲート線G2を開始行、ゲート線Gnを終了行とし、開始行から終了行の方向に偶数行のゲート線をスキャンするシフトレジスタ回路SRCe2～SRCen+1を備えている。この第2ゲートドライバ回路3は、アモルファスシリコンTFTで構成されている。

…（中略）…

【0020】

図2に示すソースドライバ回路5は、ソース極性制御信号POLに同期して出力極性を切り替え、ソース切り替え制御信号SELに同期して、画像データDATA（制御信号含む）に基づくソース信号を切り替えている。ソースドライバ回路5は、ソース線S1～Smに接続され、それぞれのソース線S1～Smにソース信号が供給される。

【0021】

図2に示すタイミング生成回路6は、垂直同期信号、水平同期信号、ドットクロック信号、データイネーブル信号を含む同期信号に基づき、ゲートドライバ制御信号を生成するゲートドライバ制御信号生成回路7、8を備えている。なお、ゲートドライバ制御信号には、スタート信号STVO、STVE及びクロック信号CKVO、CKVBO、CKVE、CKVBEが含まれる。また、ゲートドライバ制御信号生成回路7には、遅延量設定信号が供給され、出力タイミングが調整されている。

…（中略）…

【0023】

第1ゲートドライバ回路2及び第2ゲートドライバ回路3は、複数のゲート線のそれぞれに対してゲート信号である出力SROUT1～nを順次出力する複数のステージを有するシフトレジスタ回路で構成されている。複数ステージのそれぞれのシフトレジスタ回路が、前のステージのシフトレジスタ回路から出力されるゲート信号に同期して、ゲート線を駆動するトランジスタ（図示せず）のゲート電位を活性化し、クロック信号に同期してゲート信号が出力される。さらに、後のステージから出力されるゲート信号に基づき、ゲート線を駆動するトランジスタをリセットする。なお、図2では、後のステージから出力されるゲート信号の供給について図示を省略している。

【0024】

また、図2に示す画像表示装置では、画素アレイ1の左右に第1及び第2ゲートドライバ回路2、3が配置される構成を採用しているが、本発明はこれに限られず、画素アレイ1と第1及び第2ゲートドライバ回路2、3との結線が同じであれば配置は左右反対でも、左右のどちらか一方に配置されても良い。図2では、シフトレジスタ回路に供給される電源VDD、VSSは図示を省略しているが、本発明では電源VDDの有無は問わない。さらに、図2に示すブロック図では、各回路に電源電圧を供給する電源回路及びゲートドライバ回路を駆動するための電圧レベルに変換するレベルシフト回路は省略している。

…（中略）…

【0033】

次に、第1及び第2ゲートドライバ回路2、3の動作は、基本的に特許文献1で開示されている方法と同じオーバラップスキャン駆動法である。具体的に、図2に示す画像表示装置では、左側に設けた第1ゲートドライバ回路2がゲート線G1、G3、G5・・・と奇数行のゲート線を駆動し、右側に設けた第2ゲートドライバ回路3がゲート線G2、G4、G6・・・と偶数行のゲート線を駆動する。」

「【図2】

(イ) 実施の形態 2

「【0042】

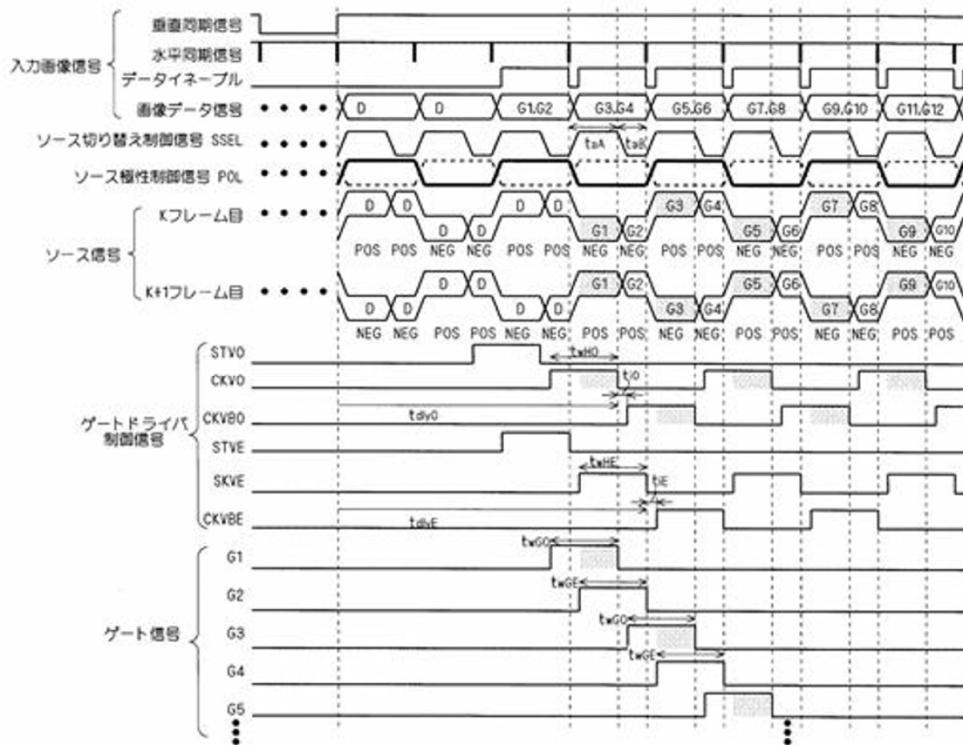

(実施の形態 2)

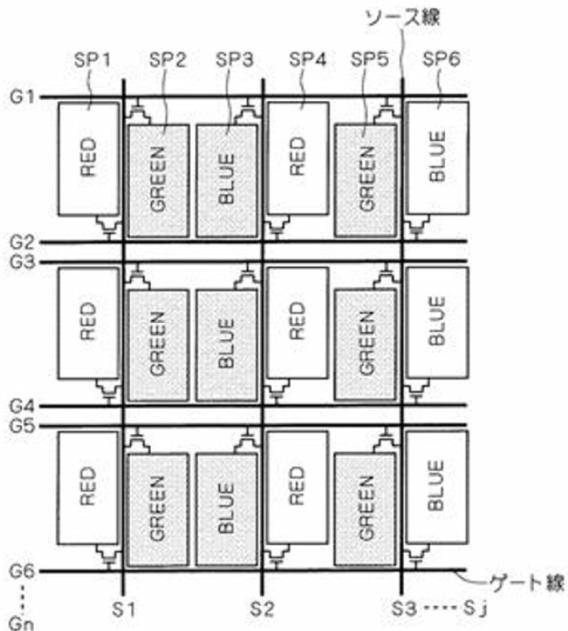

本実施の形態では、実施の形態 1 と異なり、図 4 に示すタイミングチャートで、図 5 に示す画素配置の画像表示装置を駆動している。本実施の形態に係る画像表示装置では、図 5 に示すように、同一行の画素に対して 2 本のゲート線を設けている。具体的に、図 5 の第 1 行目の R G B の画素はゲート線 G 1 に接続されたもの (SP 2, 4, 6) とゲート線 G 2 に接続に接続されたもの (SP 1, 3, 5) がある。そのため、ゲート線の数は、図 3 に示す画素配置の場合に比べ 2 倍になるが、ソース線の数は 2 分の 1 となる。

…(中略)…

【0044】

その他のタイミングは、図 1 に示すタイミングチャートと同じであり、本実

施の形態に係る画像表示装置の構成も図2に示す構成と同じである。また、本実施の形態に係る駆動方法は、非特許文献2に開示された駆動方法に実施の形態1の駆動方法を適用した駆動である。そのため、実施の形態1及び非特許文献2と重複する部分については詳細な説明を省略する。」

「【図4】

」

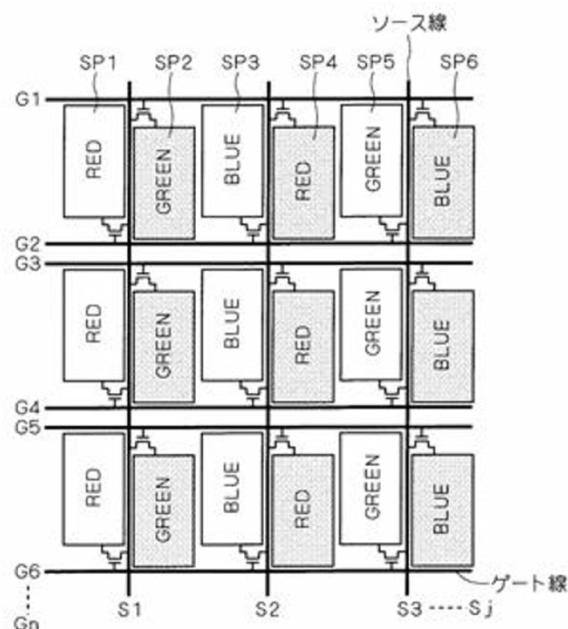

#### (ウ) 実施の形態 3

「【〇〇四八】

(実施の形態 3)

非特許文献2で開示された駆動方法は、図9に示すタイミングチャートのようにソース切り替え制御信号SSELが存在せず、ソース信号が常に同じ出力期間を有する駆動方法であった。そのため、 $n - 1$ ラインのソース信号と $n$ ラインのソース信号とが逆極性の場合、画素への充電不足が生じていた。そこで、本実施の形態に係る画像表示装置では、 $n - 1$ ラインのソース信号と $n$ ラインのソース信号とが逆極性となり充電不足が生じる画素の色を意図的に選択することで、当該充電不足により表示品位の劣化を低減している。

【〇〇四九】

具体的に、図7及び図8に、本実施の形態に係る画像表示装置の $m$ 列× $n$ 行の画素配置及びソース線及びゲート線との結線を示す。図7に示す画素配列では、ゲート線G1, G3, G5等の奇数ゲート線に、ソース線S1, S3に接続された緑画素SP2, 5とソース線S2に接続された青画素SP3とが接続されている。また、図7に示す画素配列では、ゲート線G2, G4, G6等の偶数ゲート線に、ソース線S1, S2に接続された赤画素SP1, 4とソース線S3に接続された青画素SP6とが接続されている。

【〇〇五〇】

図7に示す画素配列において、図9に示すタイミングチャートで駆動した場合、奇数ゲート線に接続された画素で充電不足となる。そのため、図7に示す画素配列では、充電不足となる画素が緑と青の半分の画素のみであり、残り赤と青の半分の画素は充電とならない。

### 【0051】

一般的に、画素への充電不足が表示品位の低下として視認されやすいのは、同じ色での濃淡が発生した場合であり、充電不足が発生しても全てサブピクセルに対して発生する場合は、色度の変化はあるものの、濃淡のムラが発生しないため視認されにくい。図5に示した画素配列では、赤、緑、青の全ての色について濃淡によるムラが発生するのに対し、図7に示した画素配列にすることで視感度の一番低い青の色についてのみ濃淡によるムラが発生するようになることで画素への充電不足による表示品位の低下を一番視認され難くしている。なお、図7に示した画素配列により生じる色度の変化については、予め予測してソースドライバ回路5の基準電圧を調整することで改善することができ、よりよい表示性能を得ることができる。

### 【0052】

本実施の形態では、画素への充電不足による表示品位の低下の改善方法として図7に示した画素配列を示したが、本発明はこれに限られず図8に示す画素配列でも良い。図8に示す画素配列では、ゲート線G1, G3, G5等の奇数ゲート線に、ソース線S1, S2に接続された赤画素SP1, 4とソース線S3に接続された青画素SP6とが接続されている。また、図8に示す画素配列では、ゲート線G2, G4, G6等の偶数ゲート線に、ソース線S1, S3に接続された緑画素SP2, 5とソース線S2に接続された青画素SP3とが接続されている。図8に示す画素配列では、充電不足となる画素が赤と青の半分の画素のみであり、残り緑と青の半分の画素は充電とならない。そのため、図7に示す画素配列と同様の効果が得られる。

### 【0053】

以上のように、本実施の形態に係る画像表示装置では、図7, 8に示す画素配列を採用することで、画素への充電不足により表示品位の低下（濃淡ムラ）を改善できる効果を有している。

### 【0054】

さらに、本実施の形態に係る画像表示装置に、実施の形態2で説明した駆動方法を採用すると、画素の充電不足が発生しないようにさせつつ、回路の動作マージンを低下させない効果を有することができる。具体的には、図7, 8に示す画素配列を採用した画像表示装置を、図4に示すタイミングチャートで駆動することで実現できる。」

「【図7】

」

イ 引用文献1の前記アの記載によれば、以下のことが認められる。（ア）実施の形態1に係る画像表示装置のブロック図（【0014】）である図2には、画素アレイ1に $m$ 列× $n$ 行の画素4が設けられること、それぞれの画素はTFTにより駆動されること、並びに、画素アレイ1の先頭（最上行）のゲート線、最終（最下行）のゲート線、最左のソース線及び最右のソース線はそれぞれG1、Gn、S1及びSmであることが示されている（【0015】）。

これを踏まえて、実施の形態3に係る画像表示装置の $m$ 列× $n$ 行の画素配置並びにソース線及びゲート線と結線を示す図7（【0049】）を見れば、図7には、「行方向に伸長するn本のゲート線G1～Gnと列方向に伸長するj本のソース線S1～Sjに対応して複数行複数列の画素が設けられ、それぞれの画素はTFTにより駆動される画素アレイ」が示されていることが理解できる。

（イ）同じく図7からは、「画素アレイの各行の画素は左から赤緑青の順に配列され、n本のゲート線G1～Gnは2本ずつが画素の1行に対応づけられ、j本のソース線S1～Sjは1本が画素の2列に対応づけられ、1本のソース線に対応づけられる2列の画素は、当該1本のソース線の左右（行方向）にそれぞれ配置されて当該1本のソース線に接続され、2本のゲート線に対応づけられる1行の画素は、当該2本のゲート線に上下（列方向）を挟まれるように配置されて当該2本のゲート線のいずれか一方に接続される」ことが見て取れる。

（ウ）実施の形態2は、タイミングチャート及び画素配置が実施の形態1と異

なるが（【0042】）、画像表示装置の構成は、図2に示す構成（実施の形態1）と同じであるから（【0044】）、実施の形態1と同様の「第1ゲートドライバ回路2」、「第2ゲートドライバ回路3」、「ソースドライバ回路5」及び「タイミング生成回路6」を備えるものと解される（図2）。

（エ）実施の形態3は、実施の形態2で説明した駆動方法を採用することができ、具体的には、図7に示す画素配列を採用した画像表示装置を、図4に示すタイミングチャートで駆動することができるから（【0054】）、実施の形態3の駆動のための構成は、実施の形態2と同様であると解される。そして、それは、実施の形態1と同様の「第1ゲートドライバ回路2」、「第2ゲートドライバ回路3」、「ソースドライバ回路5」及び「タイミング生成回路6」を備えるものである（前記（ウ））。

したがって、実施の形態3に係る画像表示装置は、図7に示す画素配列を採用した画像表示装置であって、駆動のための構成として、実施の形態1と同様の「第1ゲートドライバ回路2」、「第2ゲートドライバ回路3」、「ソースドライバ回路5」及び「タイミング生成回路6」を備え、図4に示すタイミングチャートで駆動されるものである。

（オ）以上のことと踏まえて、引用文献1の前記アの記載を整理すると、引用文献1には、実施の形態3として以下の発明（以下、「引用発明」という。）が記載されている。

「TFTにより画素を駆動する画像表示装置であって（【0014】）、行方向に伸長するn本のゲート線G<sub>1</sub>～G<sub>n</sub>と列方向に伸長するj本のソース線S<sub>1</sub>～S<sub>j</sub>に対応して複数行複数列の画素が設けられ、それぞれの画素はTFTにより駆動される画素アレイと（前記（ア））、

画素アレイの左側に配置され、ゲート線G<sub>1</sub>を開始行、ゲート線G<sub>n-1</sub>を終了行とし、開始行から終了行の方向に奇数行のゲート線をスキャンするシフトレジスタ回路SRCO<sub>1</sub>～SRCO<sub>n</sub>を備えている第1ゲートドライバ回路2と（【0024】、【0033】、【0016】）、

画素アレイの右側に配置され、ゲート線G<sub>2</sub>を開始行、ゲート線G<sub>n</sub>を終了行とし、開始行から終了行の方向に偶数行のゲート線をスキャンするシフトレジスタ回路SRC<sub>E2</sub>～SRC<sub>En+1</sub>を備えている第2ゲートドライバ回路3と（【0024】、【0033】、【0018】）、

ソース線S<sub>1</sub>～S<sub>j</sub>に接続され、それぞれのソース線S<sub>1</sub>～S<sub>j</sub>にソース信号を供給するソースドライバ回路5と（【0020】、図7、前記（ア））、

ゲートドライバ制御信号を生成するタイミング生成回路6と（【0021】）、

を備え、

第1ゲートドライバ回路2及び第2ゲートドライバ回路3のそれぞれのシフトレジスタ回路は、前のステージのシフトレジスタ回路から出力されるゲート信号に同期して、ゲート線を駆動するトランジスタのゲート電位を活性化し、

クロック信号に同期してゲート信号を出力し、後のステージから出力されるゲート信号に基づき、ゲート線を駆動するトランジスタをリセットし（【0023】）、

画素アレイの各行の画素は左から赤緑青の順に配列され、 $n$ 本のゲート線 $G_1 \sim G_n$ は2本ずつが画素の1行に対応づけられ、 $j$ 本のソース線 $S_1 \sim S_j$ は1本が画素の2列に対応づけられ、1本のソース線に対応づけられる2列の画素は、当該1本のソース線の左右（行方向）にそれぞれ配置されて当該1本のソース線に接続され、2本のゲート線に対応づけられる1行の画素は、当該2本のゲート線に上下（列方向）を挟まれるように配置されて当該2本のゲート線のいずれか一方に接続され（前記（イ））、

ゲート線 $G_1, G_3, G_5$ 等の奇数ゲート線に、ソース線 $S_1, S_3$ に接続された緑画素 $S_P 2, 5$ とソース線 $S_2$ に接続された青画素 $S_P 3$ とが接続され、ゲート線 $G_2, G_4, G_6$ 等の偶数ゲート線に、ソース線 $S_1, S_2$ に接続された赤画素 $S_P 1, 4$ とソース線 $S_3$ に接続された青画素 $S_P 6$ とが接続されている（【0049】、図7）、

画像表示装置。」

## （2）対比

本願発明と引用発明とを対比すると、以下のとおりである。

ア 引用発明の「TFTにより画素を駆動する画像表示装置」の「行方向に伸長する $n$ 本のゲート線 $G_1 \sim G_n$ と列方向に伸長する $j$ 本のソース線 $S_1 \sim S_j$ に対応して複数行複数列の画素が設けられ、それぞれの画素はTFTにより駆動される画素アレイ」と、

「画素アレイの左側に配置され、ゲート線 $G_1$ を開始行、ゲート線 $G_{n-1}$ を終了行とし、開始行から終了行の方向に奇数行のゲート線をスキャンするシフトレジスタ回路 $SRCO_1 \sim SRCO_n$ を備えている第1ゲートドライバ回路2」と、

「画素アレイの右側に配置され、ゲート線 $G_2$ を開始行、ゲート線 $G_n$ を終了行とし、開始行から終了行の方向に偶数行のゲート線をスキャンするシフトレジスタ回路 $SRCE_2 \sim SRCE_{n+1}$ を備えている第2ゲートドライバ回路3」とを合わせたものは、

本願発明の「表示パネル」に相当する。

イ 引用発明の「画素アレイ」に設けられた「複数行複数列の画素」は、

本願発明の「表示領域に配置され、第1画素行及び第2画素行を含む複数の画素」に相当する。

ウ 引用発明の「複数行複数列の画素」が対応するところの「列方向に伸長する $j$ 本のソース線 $S_1 \sim S_j$ 」は、「1本が画素の2列に対応づけられ」るものであり、一般に4本以上あることは技術常識であるから、

本願発明の「列方向に伸長され、順次に配列された第 $m-1$ （ $m$ は自然数）

データライン、第 $m$ データライン、第 $m+1$ データライン、及び第 $m+2$ データラインを含む複数のデータライン」に相当する。

エ 引用発明の「複数行複数列の画素」が対応するところの「行方向に伸長する $n$ 本のゲート線 $G_1 \sim G_n$ 」は、

本願発明の「行方向に伸長された複数のゲートライン」に相当する。

オ 引用発明は、「画素アレイ」に「画素」が「複数行」設けられ、「1行の画素は」「2本のゲート線に上下（列方向）を挟まれるように配置されて」いるから、

本願発明と同じく、「前記第1画素行は、前記第1画素行の第1側部に位置する第1ゲートラインと前記第1画素行の第2側部に位置する第2ゲートラインとの間に配置され」、「前記第2画素行は、前記第2画素行の第1側部に位置する第1ゲートラインと前記第2画素行の第2側部に位置する第2ゲートラインとの間に配置され」ているといえる。

カ 引用発明の「画素アレイの左側」は、

本願発明の「前記表示領域の第1周辺領域」に相当し、

引用発明の「画素アレイの左側に配置され」る「第1ゲートドライバ回路2」が備える「開始行から終了行の方向に奇数行のゲート線をスキヤンするシフトレジスタ回路 $SRCO_1 \sim SRCO_n$ 」のうちの隣接する2つは、

本願発明の「前記表示領域の第1周辺領域に形成され、第1画素行の第1ゲートラインにゲート信号を提供する第 $i-1$ （ $i$ は自然数）ステージ」及び「前記第 $i-1$ ステージに隣接する前記第1周辺領域に形成され、前記第2画素行の第1ゲートラインにゲート信号を提供する第 $i$ ステージ」に相当する。

キ 引用発明の「画素アレイの右側」は、

本願発明の「前記第1周辺領域に向き合う前記表示領域の第2周辺領域」に相当し、

引用発明の「画素アレイの右側に配置され」る「第2ゲートドライバ回路3」が備える「開始行から終了行の方向に偶数行のゲート線をスキヤンするシフトレジスタ回路 $SRCE_2 \sim SRCE_{n+1}$ 」のうちの隣接する2つは、

本願発明の「前記第1周辺領域に向き合う前記表示領域の第2周辺領域に形成され、前記第1画素行の第2ゲートラインにゲート信号を提供する第 $j-1$ （ $j$ は自然数）ステージ」及び「前記第 $j-1$ ステージに隣接する前記第2周辺領域に形成され、前記第2画素行の第2ゲートラインにゲート信号を提供する第 $j$ ステージ」に相当する。

### （3）一致点及び相違点

前記（2）の対比の結果をまとめると、本願発明と引用発明との一致点及び相違点は、以下のとおりである。

## ア 一致点

「表示領域に配置され、第1画素行及び第2画素行を含む複数の画素と、

列方向に伸長され、順次に配列された第 $m-1$ （ $m$ は自然数）データライン、

第 $m$ データライン、第 $m+1$ データライン、及び第 $m+2$ データラインを含む

複数のデータラインと、

行方向に伸長された複数のゲートラインと、を有し、

前記第1画素行は、前記第1画素行の第1側部に位置する第1ゲートライン

と前記第1画素行の第2側部に位置する第2ゲートラインとの間に配置され、

前記第2画素行は、前記第2画素行の第1側部に位置する第1ゲートライン

と前記第2画素行の第2側部に位置する第2ゲートラインとの間に配置され、

前記表示領域の第1周辺領域に形成され、第1画素行の第1ゲートラインに

ゲート信号を提供する第 $i-1$ （ $i$ は自然数）ステージと、

前記第 $i-1$ ステージに隣接する前記第1周辺領域に形成され、前記第2画

素行の第1ゲートラインにゲート信号を提供する第 $i$ ステージと、を含み、

前記第1周辺領域に向き合う前記表示領域の第2周辺領域に形成され、前記

第1画素行の第2ゲートラインにゲート信号を提供する第 $j-1$ （ $j$ は自然数）

ステージと、

前記第 $j-1$ ステージに隣接する前記第2周辺領域に形成され、前記第2画

素行の第2ゲートラインにゲート信号を提供する第 $j$ ステージと、を更に含む

表示パネル。」

## イ 相違点

### （ア）相違点1

本願発明は、「前記第 $i-1$ ステージと前記第 $i$ ステージとの間の前記第1

周辺領域に形成され、前記第1画素行の第2ゲートラインに印加されたハイ電

圧をロー電圧に放電する第2放電トランジスタ」と及び「前記第 $j-1$ ステージ

と前記第 $j$ ステージとの間の前記第2周辺領域に形成され、前記第2画素行の

第1ゲートラインに印加されたハイ電圧をロー電圧に放電する第1放電トラン

ジスタ」を含み、「前記第1放電トランジスタは、行方向で第2放電トランジ

スタに重ならない」のに対し、

引用発明は、放電トランジスタを含まない点。

### （イ）相違点2

本願発明では、「前記第 $m-1$ データラインと前記第 $m$ データラインとの間

の前記第1画素行の第1画素及び第2画素は、前記第 $m$ データラインに電気的

に接続され」、「前記第 $m$ データラインと前記第 $m+1$ データラインとの間の

前記第1画素行の第3画素及び第4画素は、前記第 $m+1$ データラインに電気的

に接続され」、「前記第 $m+1$ データラインと前記第 $m+2$ データラインとの間の

前記第1画素行の第5画素及び第6画素は、前記第 $m+2$ データラインに電気的

に接続され」るのに対し、

引用発明では、「1本のソース線に対応づけられる2列の画素は、当該1本

のソース線の左右（行方向）にそれぞれ配置されて当該1本のソース線に接続

され」る点。

#### (ウ) 相違点 3

本願発明では、「前記第1画素行の前記第1、第3、及び第6画素は、前記第1画素行の第1側部に位置する第1ゲートラインに電気的に接続され」、「前記第1画素行の前記第2、第4、及び第5画素は、前記第1画素行の第2側部に位置する第2ゲートラインに電気的に接続され」るのに対し、

引用発明では、「左から赤緑青の順に配列され」る「各行の画素」のうち、「ソース線S1、S3に接続された緑画素SP2、5とソース線S2に接続された青画素SP3と」が「ゲート線G1、G3、G5等の奇数ゲート線」に接続され、「ソース線S1、S2に接続された赤画素SP1、4とソース線S3に接続された青画素SP6と」が「ゲート線G2、G4、G6等の偶数ゲート線」に接続される点。

#### (4) 相違点についての判断

##### ア 相違点 1について

引用文献3の【0001】、【0006】、【0020】、【0022】、【0029】及び図1には、ゲートドライバを備えた表示装置において、複数のゲートラインの第1端部に隣接して複数の駆動ステージからなるシフトレジスタを設けるとともに、複数のゲートラインの第2端部には複数の放電トランジスタをそれぞれ接続し、複数の駆動ステージの制御端子及び複数の放電トランジスタの制御電極が直後のゲートラインのゲート信号を受信することで、対応するゲートラインをゲートオフ電圧まで放電させ、各駆動ステージを正常にリセットさせる技術が記載されている。

一方、引用発明は、「第1ゲートドライバ回路2」及び「第2ゲートドライバ回路3」を備えた「画像表示装置」であって、複数の「ゲート線」の一方の端部には「シフトレジスタ回路」が設けられ、「後のステージから出力されるゲート信号に基づき、ゲート線を駆動するトランジスタをリセットするもの」である。

そうすると、引用発明において、ゲート線を駆動するトランジスタを正常にリセットするために、引用文献3に記載された前記技術を採用することは、当業者であれば容易に想到し得たことである。

そのようにした場合、複数のゲート線の「シフトレジスタ回路」が設けられるのとは反対側の端部に、「放電トランジスタ」をそれぞれ接続することとなるから、「画素アレイの左側に配置され」る「シフトレジスタ回路SRCO1～SRCOn」と接続される「奇数行のゲート線」を放電させるために、「画素アレイの右側」に「放電トランジスタ」を設けることになる。また、「画素アレイの右側に配置され」る「シフトレジスタ回路SRCEn+1～SRCEn+1」と接続される「偶数行のゲート線」を放電させるために、「画素アレイの左側」に「放電トランジスタ」を設けることとなる。

ここで、例えば、引用文献6の【0009】、【0010】、【0076】、【0077】、図6及び図17ないし図19や、引用文献7の【0012】、

【0013】及び図1を参照すれば分かるように、表示装置における狭額縫化は、優先日前に周知の課題である。このことを考慮すれば、引用発明において「画素アレイの右側」及び「画素アレイの左側」に「放電トランジスタ」をそれぞれ設ける際、額縫の幅が大きくなないように、「画素アレイの右側」に設ける「放電トランジスタ」は「シフトレジスタ回路SRC E<sub>2</sub>～SRC E<sub>n+1</sub>」の間に、「画素アレイの左側」に設ける「放電トランジスタ」は「シフトレジスタ回路SRC O<sub>1</sub>～SRC O<sub>n</sub>」の間に、それぞれ配置するようにすることは、当業者が適宜採用し得る設計的事項にすぎない。また、「画素アレイの右側」及び「画素アレイの左側」にそれぞれ設けられる「放電トランジスタ」を、行方向で重ならないようにすることも、部材の最適な配置を検討する上で適宜採用し得る設計的事項にすぎない。

#### イ 相違点2について

例えば、引用文献2の【0070】及び図3や、引用文献4の【0034】及び図3に示されるように、1本のソース線を2列の画素に対応させる画素配列として、ある画素行では、2本のソース線の間に位置する2つの画素を、両方とも右側のソース線に接続するようにし、次の画素行では、2本のソース線の間に位置する2つの画素を、両方とも左側のソース線に接続するようにしたものは、優先日前に周知である。

引用発明において、「1本のソース線に対応づけられる2列の画素は、当該1本のソース線の左右（行方向）にそれぞれ配置されて当該1本のソース線に接続され」ている画素配列に代えて、前記周知の画素配列を採用し、ソース線S<sub>m-1</sub>とソース線S<sub>m</sub>の間に位置する2つの画素を、両方ともソース線S<sub>m</sub>に接続することは、当業者が容易に行い得ることである。

#### ウ 相違点3について

引用文献1には、実施の形態3（すなわち、引用発明）について、「本実施の形態では、画素への充電不足による表示品位の低下の改善方法として図7に示した画素配列を示したが、本発明はこれに限られず図8に示す画素配列でも良い。」（【0052】）と記載されているから、引用発明の画素配列を変更することは、当業者が適宜行い得る設計事項にすぎない。

例えば、引用文献1の図7（前記（1）ア（ウ））において、ソース線「S<sub>1</sub>」並びにそれに接続された画素「SP<sub>1</sub>」及び「SP<sub>2</sub>」をなくし、ソース線「S<sub>2</sub>」、「S<sub>3</sub>」…を改めて「S<sub>1</sub>」、「S<sub>2</sub>」…とし、画素「SP<sub>3</sub>」、「SP<sub>4</sub>」、「SP<sub>5</sub>」、「SP<sub>6</sub>」…を改めて画素「SP<sub>1</sub>」、「SP<sub>2</sub>」、「SP<sub>3</sub>」、「SP<sub>4</sub>」…とすれば、画素「SP<sub>1</sub>」、「SP<sub>3</sub>」及び「SP<sub>6</sub>」がゲート線「G<sub>1</sub>」に接続され、画素「SP<sub>2</sub>」、「SP<sub>4</sub>」及び「SP<sub>5</sub>」がゲート線「G<sub>2</sub>」に接続されることが明らかである。

#### （5）理由2についてのまとめ

以上のとおりであるから、本願発明は、引用文献1に記載された発明（引用発明）、引用文献3に記載された技術、引用文献6や引用文献7に記載された

周知の課題、引用文献2や引用文献4に示された周知の画素配列及び引用文献1に記載された事項に基づいて、当業者が容易に発明をすることができたものであるから、特許法第29条第2項の規定により特許を受けることができない。

## 5 むすび

第1次補正は、当初明細書等に記載した事項の範囲内においてしたものではないから、特許法第17条の2第3項に規定する要件を満たしていない。

したがって、本願は拒絶をするべきものである。

また、本願発明は、引用文献1ないし引用文献4、引用文献6及び引用文献7に記載された発明に基づいて、当業者が容易に発明をすることができたものであるから、特許法第29条第2項の規定により特許を受けることができない。

したがって、他の請求項に係る発明について検討するまでもなく、本願は拒絶するべきものである。

よって、結論のとおり審決する。

令和2年2月3日

審判長 特許庁審判官 中塚 直樹

特許庁審判官 小林 紀史

特許庁審判官 濱野 隆

(行政事件訴訟法第46条に基づく教示)

この審決に対する訴えは、この審決の謄本の送達があった日から30日（附加期間がある場合は、その日数を附加します。）以内に、特許庁長官を被告として、提起することができます。

審判長 中塚 直樹

出訴期間として在外者に対し90日を附加する。

〔審決分類〕 P 18. 572-WZ (G09G)

55

121

審判長 特許庁審判官 中塚 直樹 8908

特許庁審判官 濱野 隆 9108

特許庁審判官 小林 紀史 8707